I remember somebody getting excited about the 6809 at the Coventry Computer Club back in 1979.

I have wanted to learn just enough about the 6809 assembly language to try it out.

I need an Emulator, Assembler, Datasheet and hardware to run some code on.

This site had a lot of links: http://atjs.mbnet.fi/mc6809/index.html - 2024/01/21 - URL not found

I was told Dave Dunsfields work has been useful.

Dunfield Development Services

https://dunfield.themindfactory.com/dds/lang.htm

https://dunfield.themindfactory.com/

and http://dunfield.classiccmp.org/

https://github.com/doug-h-rice/virtual-multicomp has virtual6809 with tools

I tried this emulator and monitor. It seems to be what I wanted. It can load my assembled code and single step through it.

http://atjs.mbnet.fi/mc6809/6809Emulators/6809.zip - URL dead on 2024/01/21

This was easy to build using Fabrice Bellard's TCC and GCC on Linux.

I modified it to run a command line emulator that loads and runs 6809 code.

The 6809 code reads and writes to a virtual UART which maps to STDIN and STDOUT in the command line program.

http://www.dougrice.plus.com/dev/asm6809/virtualMultiComp/

and

https://github.com/doug-h-rice/virtual-multicomp

It boots Grant's modified BASIC for 6809 and boots my assembled code doug.s19.

I found an assembler called as09, but cannot remember which one.

For Windows, I downloaded asm6809-2.12-w64 from http://www.6809.org.uk/

For Linux and also for Windows I can use as9

https://github.com/doug-h-rice/virtual-multicomp has as9 and

Grand Searle's Multicomp for 6809 provides hardware to run my 6809 code.

He does an FPGA version and an excellent tutorial to follow.

http://searle.wales/ FPGA - Multicomp on Cyclone11 - 6809

EBAY and AMAZON has some cyclone11 boards for sale. They provide enough to try out VHDL and VERILOG and Grant Searle used one to host his SBC in an FPGA

Some files:- http://www.dougrice.plus.com/dev/asm6809/

This page works towards a build chain batch file that can be used to assemble the 6809 code and upload it to the emulator and FPGA boards.

I followed Grant Searle's excellent tutorial on configuring his FPGA design.

Building the FPGA .sof file takes 5 to 7 minutes. It would be nice to update the ROM a little quicker.

I found out how to modify the FPGA design to upload new 6809 code to the ROM without a full rebuild of the .sof file.

You need to install the Altera Quartus 13.0 free version.

C:/altera/13.0sp1web/Multicomp/Microcomputer

Grant's website has spawned many projects of Multicomp SBC.

EBAY has an Cyclone IV board listed

Doug Gilliliand has ported Grant's code to many FPGA boards.

https://github.com/douggilliland - it was a massive 700MB zip file. It ports the Multicomp to many FPGA boards.

This is a rework.

https://hackaday.io/LandBoards https://github.com/land-boards - A vast download. It provided an enjoyable challenge. http://land-boards.com/blwiki/index.php?title=Main_Page https://www.youtube.com/channel/UCTemcBf9UzLwhLCaOMRJEqQ/videos

It takes a few minutes to build the code to get to the .sof file that is uploaded to the FPGA.

It is possible to set up the ROM and RAM so these can be modified using JTAG without a full rebuild.

Using a batch file it is possible to assemble, relocate the code and upload it to the FPGA in a few seconds.

The hex file needs the addresses adjusting as the ROM starts at $E000 to $FFFF.

A simple C program was written to do this. It was modfied from the hexload code used on my virtual_multicomp.

hexROMadjust.c - adjusts addresses and amends checksum in hex file

****************************************************** * doug.asm

Try out of 6809 assembler

The cpu resets $FFFF

Objectives

set up vectors run start up code run simple code

usage:

./as9 dougs6809dabble.asm -l s19

6809/a.out doug.s19

asm6809 --hex -l doug.lst -o doug.hex dougs6809dabble.asm

I need a utility to move the hex file. The hex file is abosulte but I need to split the file to load into the devices The ROM is at 0XE000 to 0XFFFF in the memory map but is at 0X0000 to 0X1FFF in the device. The RAM is at 0X0000 to 0X3FFF in the memory map but is at 0X0000 to 0X3FFF in the device.

******************************************************

rem do_dougs6809dabble.asm.bat rem rem asm6809 --hex -l doug.lst -o doug.hex doug.asm asm6809 --hex -l doug.lst -o doug.hex dougs6809dabble.asm rem pause

I wrote hexROMadjust to allow for ROM @0XE000 to 0XFFFF needs addesses from 0X0000 to 0X01FF

type doug.hex | hexROMadjust.exe type doug.hex | hexROMadjust.exe > doug_2f.hex hexROMadjust doug.hex > doug_2f.hex

REM Doug Gilliland's https://github.com/land-boards - A challenge to get working

copy doug_1f.hex C:\altera\13.0sp1web\M6809_VGA_PS2_UART_IntRAM(16K)\output_files copy doug_2f.hex C:\altera\13.0sp1web\M6809_VGA_PS2_UART_IntRAM(16K)\output_files

REM Grant Searle's

copy doug_1f.hex C:\altera\13.0sp1web\Multicomp\Microcomputer\output_files copy doug_2f.hex C:\altera\13.0sp1web\Multicomp\Microcomputer\output_files

pause

With the altera\13.0sp1web installed it is possible to modify the ROM contents without rebuilding the .sof file.

You can use the GUI, but it must be possible to automate this. This is how.

Command line update ROM contents of Grants Multicomp rem cd C:\altera\13.0sp1web\Multicomp\Microcomputer> C:\altera\13.0sp1web\quartus\bin\quartus_stp -t C:\altera\13.0sp1web\Multicomp\Microcomputer\MicrocomputerCmd.qsf

pause

It can take a long time to build the FPGA code. These builds typically take 5 to 7 minutes to build the .sof file used to load the FPGA.

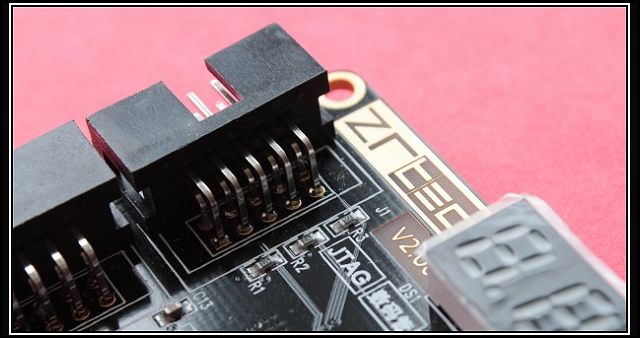

It is possible to use the JTAG and USBblaster cable to upload new ROM images without a full FPGA build, if the ROM is set up correctly in the build.

******************************************************* modify ROM so it can be modified via the USB Blaster. M6809_MY_ROM.vhd GENERIC MAP ( .. init_file => "../../Microcomputer/output_files/doug_1f.hex", .. lpm_hint => "ENABLE_RUNTIME_MOD=YES,INSTANCE_NAME=ROM1", .. operation_mode => "ROM", )

When you use the GUI you get this debug.

Info (261000): get_editable_mem_instances -hardware_name "USB-Blaster \[USB-0\]" -device_name "@1: EP2C5 (0x020B10DD)" Info (261000): begin_memory_edit -hardware_name "USB-Blaster \[USB-0\]" -device_name "@1: EP2C5 (0x020B10DD)" Info (261000): get_editable_mem_instances -hardware_name "USB-Blaster \[USB-0\]" -device_name "" Info (261000): begin_memory_edit -hardware_name "USB-Blaster \[USB-0\]" -device_name "" Info (261000): get_editable_mem_instances -hardware_name "USB-Blaster \[USB-0\]" -device_name "@1: EP2C5 (0x020B10DD)" Info (261000): begin_memory_edit -hardware_name "USB-Blaster \[USB-0\]" -device_name "@1: EP2C5 (0x020B10DD)" Info (261000): update_content_to_memory_from_file -instance_index 0 -mem_file_path "C:/altera/13.0sp1web/Multicomp/Microcomputer/output_files/doug_1f.hex" -mem_file_type "" Info (261000): write_content_to_memory -instance_index 0 -content "<value string is too long to be displayed>" -content_in_hex -start_address 0 -word_count 8192

There must use command line commands, istead of using the GUI.

The FPGA has the .sof file loaded and the ROM is included in the .sof file. It takes 5 to 7 minutes to rebuild the .sof file.

However with the altera\13.0sp1web installed use the GUI to modify the ROM contents without rebuilding the .sof file.

You can use the GUI, but it is possible to automate this using the command line using quartus_stp.

The JTAG cables and the Signal Tap provide a way.

#C:\altera\13.0sp1web\quartus\bin\quartus_stp -t

I set up C:\altera\13.0sp1web\Multicomp\MicrocomputerMicrocomputerCmd.qsf based on the debug comment.

C:\altera\13.0sp1web\Multicomp\MicrocomputerMicrocomputerCmd.qsf

#end_memory_edit

begin_memory_edit -hardware_name "USB-Blaster \[USB-0\]" -device_name "@1: EP2C5 (0x020B10DD)" get_editable_mem_instances -hardware_name "USB-Blaster \[USB-0\]" -device_name "@1: EP2C5 (0x020B10DD)" update_content_to_memory_from_file -instance_index 0 -mem_file_path "C:/altera/13.0sp1web/Multicomp/Microcomputer/output_files/doug_1f.hex" -mem_file_type "HEX" end_memory_edit

# C:\altera\13.0sp1web\quartus\bin\quartus_stp # Quartus II 32-bit SignalTap II # Version 13.0.1 Build 232 06/12/2013 Service Pack 1 SJ Web Edition # Copyright (C) 1991-2013 Altera Corporation # quartus_stp -s # quartus_stp --tcl_eval <tcl command>

# C:\Users\doug>C:\altera\13.0sp1web\quartus\bin\quartus_stp -s

C:\altera\13.0sp1web\quartus\bin\quartus_stp -t

Here is how to load .sof files into the Cyclone 11 FPGA using USB-blaster using quartus_pgm

rem BAUD rate either 115200 or 9600

Use this to find the USBblaster

C:\altera\13.0sp1web\quartus\bin\quartus_pgm --auto

Lets look at each parameter. The p; in the -o option is important and not a typo! p; - program.

C:\altera\13.0sp1web\quartus\bin\quartus_pgm -c "USB-Blaster [USB-0]" -m jtag -o p;C:\altera\13.0sp1web\Multicomp\Microcomputer\output_files\Microcomputer_6809_MYROM_9600.sof@1

rem Microcomputer_6809_MYROM_9600

C:\altera\13.0sp1web\quartus\bin\quartus_pgm -c "USB-Blaster [USB-0]" -m jtag -o p;C:\altera\13.0sp1web\Multicomp\Microcomputer\output_files\Microcomputer_6809_MYROM_9600.sof@1

REM OSI 6502 BASIC VERSION 1.0 REV 3.2

C:\altera\13.0sp1web\quartus\bin\quartus_pgm -c "USB-Blaster [USB-0]" -m jtag -o p;C:\altera\13.0sp1web\Multicomp\Microcomputer\output_files\Microcomputer_6502_115200.sof

REM Microcomputer_z80_ROM_115200.sof x80 test.hex built using SDCC, BAUD 115200

C:\altera\13.0sp1web\quartus\bin\quartus_pgm -c "USB-Blaster [USB-0]" -m jtag -o p;C:\altera\13.0sp1web\Multicomp\Microcomputer\output_files\Microcomputer_z80_ROM_115200.sof

rem Z80 BASIC Ver 4.7b

C:\altera\13.0sp1web\quartus\bin\quartus_pgm -c "USB-Blaster [USB-0]" -m jtag -o p;C:\altera\13.0sp1web\Multicomp\Microcomputer\output_files\Microcomputer_z80_115200.sofpause

*************************************************

* PC

* U

* S

* Y

* X

* D { A,B

* DP

* CC

*************************************************

* ../ROMS/6809/EXT_BASIC_NO_USING.hex

*